### LX8380 Data Sheet

Lexra, Inc.

**Revision 1.4**

November 21, 2001

Lexra Proprietary and Confidential

LX8380 Data Sheet Revision 1.4.

*Lexra Proprietary and Confidential* Copyright © 2001 Lexra, Inc. ALL RIGHTS RESERVED

MIPS, MIPS16, MIPS ABI, MIPS I, MIPS II, MIPS IV, MIPS V, MIPS32, R3000, R4000, and other MIPS common law marks are trademarks and/or registered trademarks of MIPS Technologies, Inc. Lexra, Inc. is not associated with MIPS Technologies, Inc. in any way.

SmoothCore and Radiax are trademarks of Lexra, Inc.

## **Table of Contents**

| 1. | Proc | luct Ov  | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 |

|----|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 1.1. | Introdu  | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 |

|    | 1.2. | LX838    | 0 Processor Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 |

|    | 1.3. | System   | Level Building Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 |

|    |      | 1.3.1.   | Simple Memory Management Unit (SMMU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 |

|    |      | 1.3.2.   | Local Memory Interface (LMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 |

|    |      | 1.3.3.   | Coprocessor Interface (CI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 |

|    |      | 1.3.4.   | Custom Engine Interface (CEI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6 |

|    |      | 1.3.5.   | Cache Bus (CBUS) Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 |

|    |      | 1.3.6.   | Lexra Bus Controller (LBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 |

|    |      | 1.3.7.   | Block Move Controller (BMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6 |

|    |      | 1.3.8.   | EJTAG Debug Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 |

|    |      | 1.3.9.   | Building Block Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 |

|    | 1.4. | RTL C    | ore & SmoothCore Licensing Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7 |

|    | 1.5. |          | ool Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 2. | Arcl | nitectur | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 |

|    | 2.1. |          | are Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|    | 2.1. |          | Stage Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|    | 2.2. |          | Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|    | 2.4. |          | Control Coprocessor (CP0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|    | 2.5. | •        | erformance Context Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|    | 2.0. | 2.5.1.   | New Context Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|    |      | 2.5.2.   | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|    |      | 2.5.3.   | Determining the Number of Contexts in Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|    |      | 2.5.4.   | Initiation of Context Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|    |      | 2.5.5.   | CSW Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|    |      | 2.5.6.   | LW.CSW, LT.CSW and LQ.CSW Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|    |      | 2.5.7.   | WD[.CSW] Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|    |      | 2.5.8.   | WDLW.CSW, WDLT.CSW and WDLQ.CSW Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|    |      | 2.5.9.   | Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|    |      | 2.5.10.  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|    |      | 2.5.11.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|    |      | 2.5.12.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|    |      | 2.5.13.  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| 3. | RIS  |          | ramming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| 5. | 3.1. | -        | ary of Basic RISC Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|    | 5.1. | 3.1.1.   | ALU Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|    |      | 3.1.2    | Load and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|    |      | 3.1.3.   | Conditional Move Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|    |      | 3.1.4.   | Branch and Jump Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|    |      | 3.1.5.   | Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|    |      | 3.1.6.   | Coprocessor Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|    | 3.2. |          | e Extension Using the Custom Engine Interface (CEI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|    | 3.3. |          | Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|    | 2.2. | Simple   | 1. Letter J 1. Luna Sentence Chite monomorphism m |   |

|    | 3.4.                         | Exception Processing                                         |    |

|----|------------------------------|--------------------------------------------------------------|----|

|    |                              | 3.4.1. Exception Processing Registers                        |    |

|    |                              | 3.4.2. Exception Processing: Entry and Exit                  |    |

|    | 3.5.                         | Low-Overhead Prioritized Interrupts                          |    |

|    | 3.6.                         | Coprocessors                                                 |    |

| 4. | Inst                         | ruction Extensions                                           |    |

|    | 4.1.                         | Context Switch and Data Transfer Operations                  |    |

|    | 4.2.                         | Bit Field Processing Operations                              |    |

|    | 4.3.                         | Cross Context Access Operations                              |    |

|    | 4.4.                         | Checksum Addition                                            |    |

|    | 4.5.                         | LX8380 Instruction Summary                                   |    |

| 5. | Con                          | processor Interface                                          | 59 |

|    | 5.1.                         | Attaching a Coprocessor Using the Coprocessor Interface (CI) |    |

|    | 5.2.                         | Coprocessor Interface (CI) Signals                           |    |

|    | 5.3.                         | Coprocessor Write Operations                                 |    |

|    | 5.4.                         | Coprocessor Read Operations                                  |    |

|    | 5.5.                         | Coprocessor Interface and Pipeline Stages                    |    |

|    | 5.5.                         | 5.5.1. Pipeline Holds                                        |    |

|    |                              | 5.5.2. Pipeline Invalidation                                 |    |

|    |                              | -                                                            |    |

| 6. |                              | al Memory                                                    |    |

|    | 6.1.                         | Local Memory Overview                                        |    |

|    | 6.2.                         | Cache Control Register: CCTL                                 |    |

|    | 6.3.                         | CACHE Instruction                                            |    |

|    | 6.4.                         | Instruction Cache (ICACHE) LMI                               |    |

|    | 6.5.                         | Instruction Memory (IMEM) LMI                                |    |

|    | 6.6. Data Cache (DCACHE) LMI |                                                              |    |

|    | 6.7.                         | Scratch Pad Data Memory (DMEM) LMI                           | 75 |

| 7. | CBU                          | US Interface                                                 | 77 |

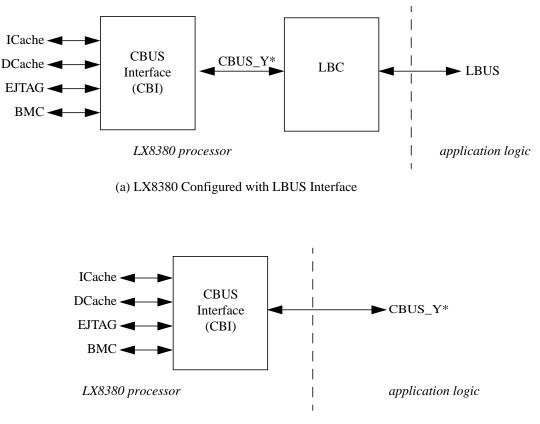

|    | 7.1.                         | System Interface Configuration                               | 77 |

|    | 7.2.                         | CBUS Interface Write Buffer and Out-of-Order Processing      | 78 |

|    | 7.3.                         | CBUS Line Read Interleave Order                              | 78 |

|    | 7.4.                         | CBUS Byte Alignment                                          | 79 |

|    | 7.5.                         | CBUS Interface Signal List                                   |    |

|    | 7.6.                         | CBUS Transaction Types                                       |    |

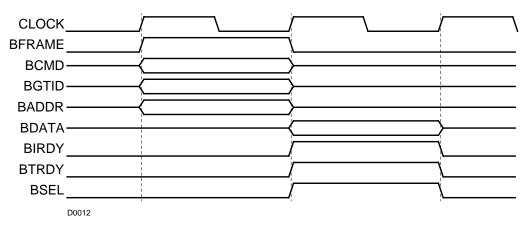

|    | 7.7.                         | CBUS Protocol                                                |    |

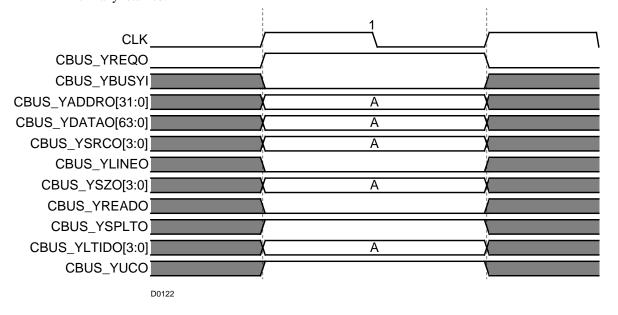

|    | 7.8.                         | CBUS Transaction Timing Diagrams                             |    |

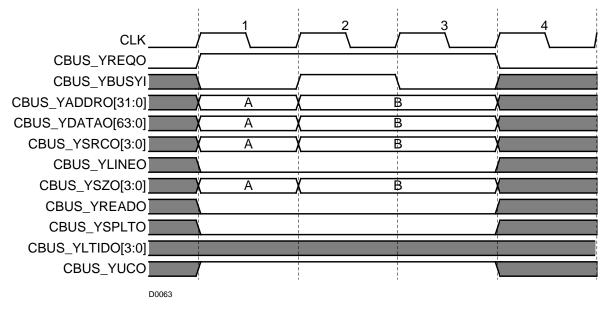

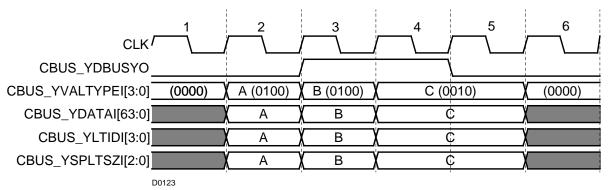

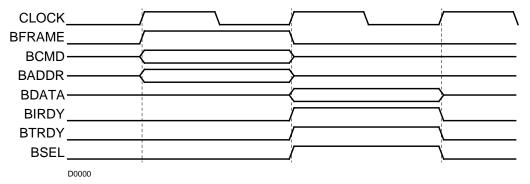

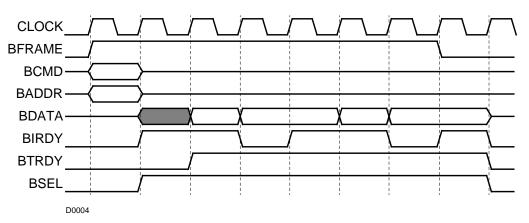

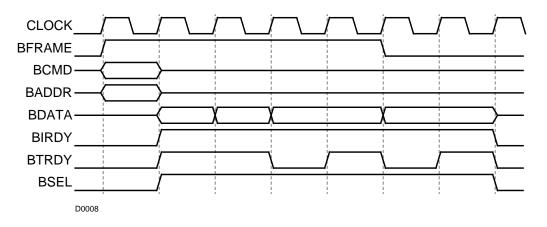

|    |                              | 7.8.1. Back-to-Back Single Writes with Busy                  |    |

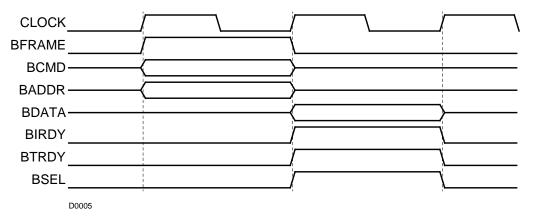

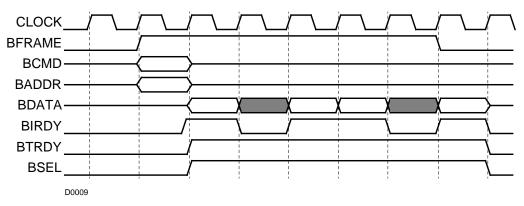

|    |                              | 7.8.2. Line Writes                                           |    |

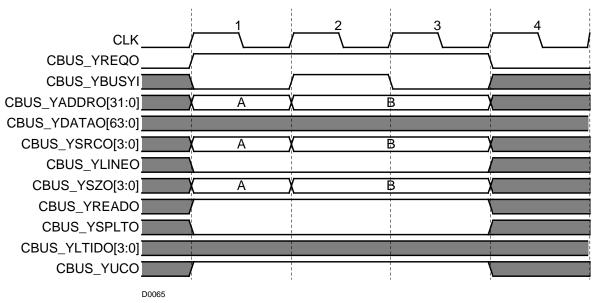

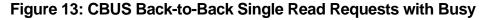

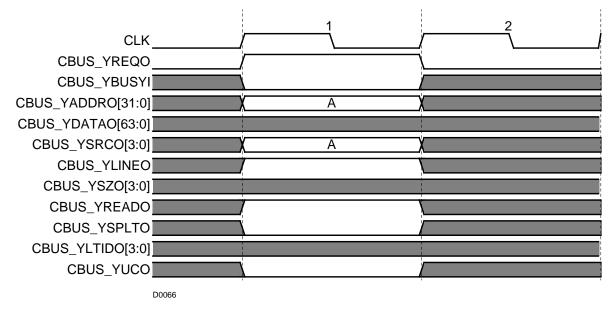

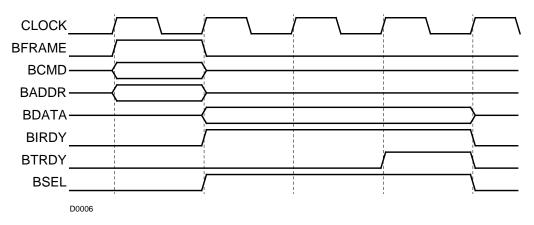

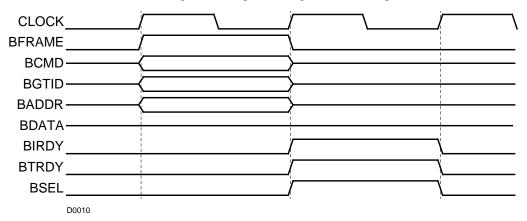

|    |                              | 7.8.3. Back-to-Back Single Read Requests with Busy           |    |

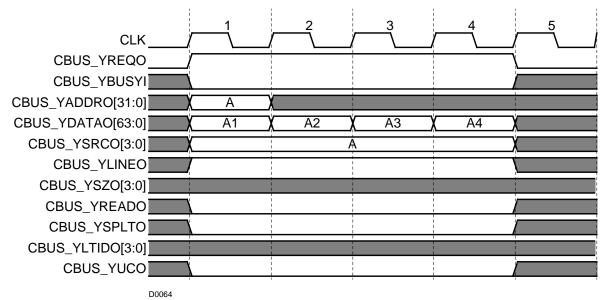

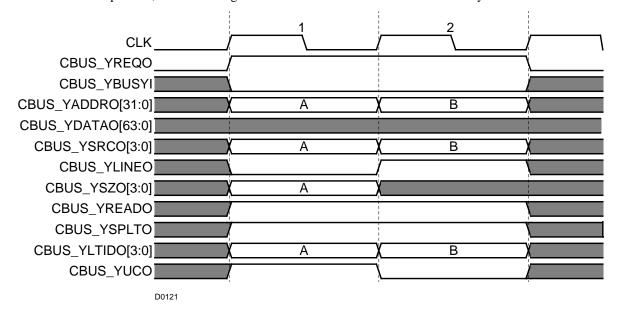

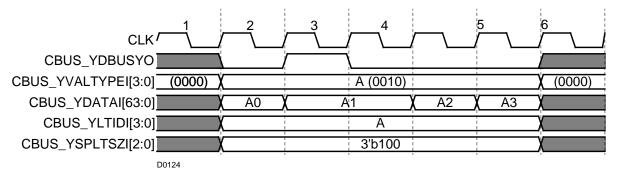

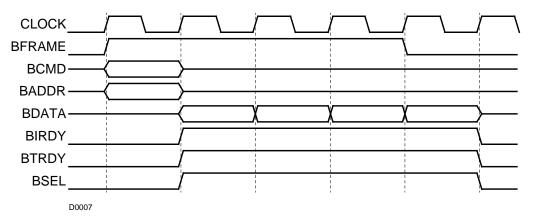

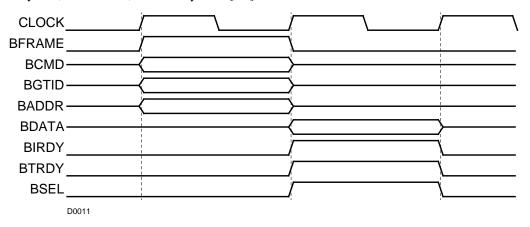

|    |                              | 7.8.4. Line Read Request                                     |    |

|    |                              | 7.8.5. Split Read Request                                    |    |

|    |                              | 7.8.6. Write with Split Read Request                         |    |

|    |                              | 7.8.7. Returning Read Data                                   |    |

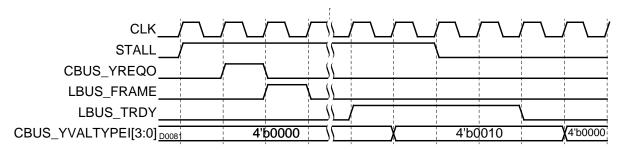

|    |                              | 7.8.8. Latency of CBUS Transactions                          |    |

| 8. | Lexi                         | ra System Bus (LBUS)                                         |    |

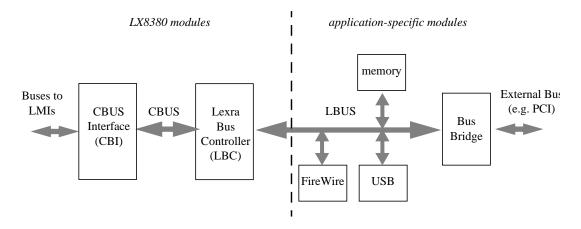

| -  | 8.1.                         | Connecting the LX8380 to Internal Devices                    |    |

|    | 8.2.                         | Terminology                                                  |    |

|    | 8.3.                         | Bus Operations                                               |    |

|    |                              | 8.3.1. Single Data Read                                      |    |

|    |                              |                                                              |    |

|    |       | 8.3.2.    | Line Read                              | 89    |

|----|-------|-----------|----------------------------------------|-------|

|    |       | 8.3.3.    | Burst Read                             | 89    |

|    |       | 8.3.4.    | Single Data Write                      | 90    |

|    |       | 8.3.5.    | Line Write                             | 90    |

|    |       | 8.3.6.    | Burst Write                            | 90    |

|    |       | 8.3.7.    | Split Read                             | 90    |

|    |       | 8.3.8.    | Write Split Read                       | 90    |

|    |       | 8.3.9.    | Split Data                             | 90    |

|    | 8.4.  | Signal I  | Descriptions                           | 91    |

|    | 8.5.  | LBUS C    | Commands                               | 92    |

|    | 8.6.  | LBUS E    | Byte Alignment                         | 93    |

|    | 8.7.  | Split Tra | ansactions                             | 93    |

|    | 8.8.  | Lexra B   | us Controller                          | 94    |

|    |       | 8.8.1.    | LBC Commands                           | 95    |

|    |       | 8.8.2.    | Write Buffer                           |       |

|    |       | 8.8.3.    | LBC Read Buffer                        | 95    |

|    | 8.9.  | Transac   | tion Descriptions                      |       |

|    |       | 8.9.1.    | Single Data Read with No Waits         |       |

|    |       | 8.9.2.    | Single Data Read with Target Wait      |       |

|    |       | 8.9.3.    | Line Read with No Waits                |       |

|    |       | 8.9.4.    | Line Read with Target Waits            |       |

|    |       | 8.9.5.    | Line Read with Initiator Waits         |       |

|    |       | 8.9.6.    | Burst Read                             |       |

|    |       | 8.9.7.    | Single Data Write with No Waits        |       |

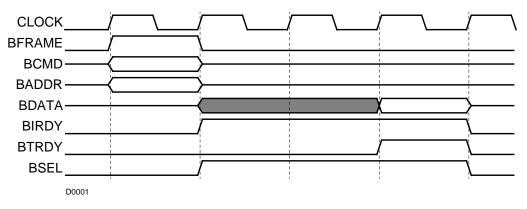

|    |       | 8.9.8.    | Single Data Write with Waits           |       |

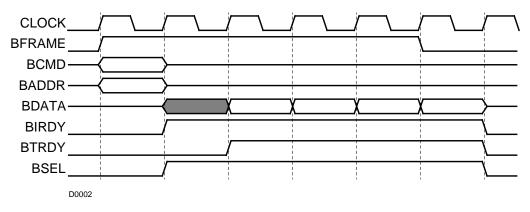

|    |       | 8.9.9.    | Line Write with No Waits               |       |

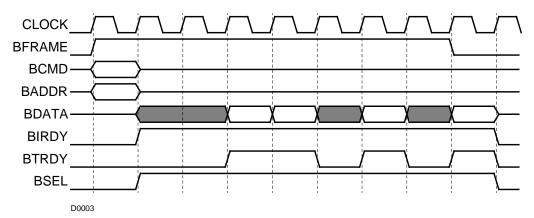

|    |       |           | Line Write with Target Waits           |       |

|    |       |           | Line Write with Initiator Waits        |       |

|    |       |           | Burst Write                            |       |

|    |       | 8.9.13.   | - F                                    |       |

|    |       | 8.9.14.   | · · · · · · · · · · · · · · · · · · ·  |       |

|    | 0.10  | 8.9.15.   | 1                                      |       |

|    |       |           | g Rules with Split Transactions        |       |

|    |       | -         | gnals                                  |       |

|    | 8.12. |           | ion                                    |       |

|    |       |           | LBUS Rules                             |       |

|    | 0.12  |           | LBC Behavior                           |       |

|    |       |           | ting the LBC to LBUS                   |       |

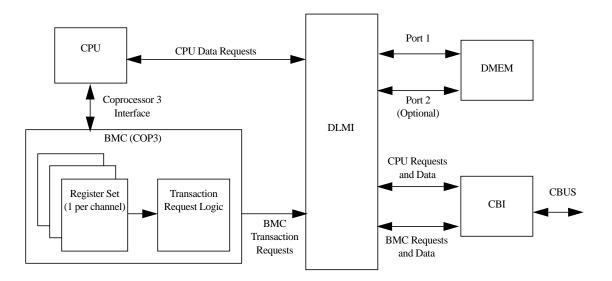

| 9. | Block | s Move    | Controller (BMC)                       | 109   |

|    | 9.1.  | BMC O     | verview                                | 109   |

|    | 9.2.  | Transfer  | rs                                     | 110   |

|    | 9.3.  |           | tions                                  |       |

|    | 9.4.  | Transac   | tion Sequence Due to Transfer Class    | . 111 |

|    | 9.5.  |           | er-Channel Registers                   |       |

|    | 9.6.  |           | lobal Registers                        |       |

|    | 9.7.  |           | nnel Register Set Selection            |       |

|    | 9.8.  |           | r Completion                           |       |

|    | 9.9.  |           | MC arbitration                         |       |

|    | 9.10. |           | e Responsibility for Transfer Requests |       |

|    | 9.11. | Example   | e Transfer Flow                        | 116   |

| 10. EJT | AG Debug                                                         | 119 |

|---------|------------------------------------------------------------------|-----|

| 10.1.   | Overview                                                         |     |

|         | 10.1.1. IEEE JTAG-Specific Pinout                                |     |

| 10.2.   | Program Counter (PC) Trace                                       |     |

|         | 10.2.1. PC Trace DCLK - Debug Clock                              |     |

|         | 10.2.2. PC Trace PCST - Program Counter Status Trace             |     |

|         | 10.2.3. PC Trace TPC - Target Program Counter                    |     |

|         | 10.2.4. Single-Processor PC Trace Pinout                         |     |

|         | 10.2.5. Vectored Interrupts and PC Trace                         |     |

|         | 10.2.6. Demultiplexing of TDO and TDI During PC Trace            |     |

| 10.3.   | Data Break Exceptions for LX8380                                 |     |

|         | 10.3.1. Data Break Data Matches on LBus Split Transactions       |     |

|         | 10.3.2. Data Breaks on Write Descriptor Accesses                 |     |

|         | 10.3.3. Support for the Load-Twin Instruction                    |     |

| Appendi | ix A. Instruction Formats                                        |     |

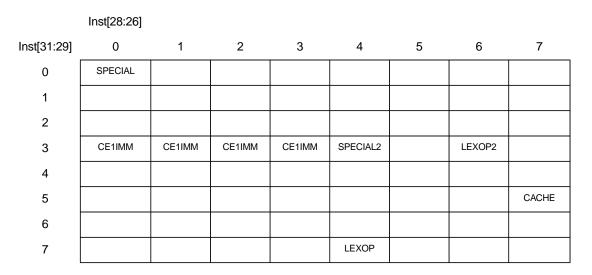

| A.1.    | Major Opcodes                                                    |     |

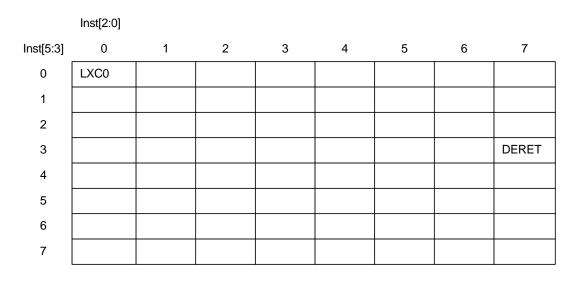

| A.2.    | LEXOP2 Instructions                                              |     |

| A.3.    | COP0 Instructions                                                |     |

| A.4.    | SPECIAL Instructions                                             |     |

| Appendi | ix B. Lconfig Forms                                              |     |

|         | Configuration Options for the LX8380 Processor                   |     |

| Appendi | ix C. Port Descriptions                                          |     |

| Appendi | ix D. Pipeline Stalls                                            |     |

| D.1.    | Stall Definitions                                                |     |

| D.2.    | Instruction Groupings                                            |     |

| D.3.    | Non-Sequential Program Flow Issue Stalls                         |     |

| D.4.    | Load/Store Rules                                                 |     |

| D.5.    | Mac Ops interlock matrix                                         |     |

| D.6.    | MVCz Stall                                                       |     |

| D.7.    | TLBW Stall                                                       |     |

| D.8.    | MOVECX Stall                                                     |     |

| D.9.    | MMU Stalls                                                       |     |

| D.10    | Cache Miss Stalls                                                |     |

| D.11    | . Pipeline Diagrams for Non-Sequential Program Flow Issue Stalls |     |

|         | . Pipeline Diagram for Mac Ops Interlock Stall                   |     |

| D.13    | . Pipeline Diagram for MVCz Stall                                |     |

|         | . Pipeline Diagram for TLBW Stall                                |     |

|         | . Pipeline Diagrams for DTLB Stalls                              |     |

|         | . Pipeline Diagrams for Cache Misses                             |     |

## **List of Tables**

| Table 1:  | EDA Tool Support                             | 7    |

|-----------|----------------------------------------------|------|

| Table 2:  | CP0 Registers                                | . 10 |

| Table 3:  | Extended CP0 Registers                       | . 10 |

| Table 4:  | Context Status Register Detail               | . 13 |

| Table 5:  | Scheduler Ports                              | . 16 |

| Table 6:  | ALU Instructions                             | . 22 |

| Table 7:  | Load and Store Instructions                  | . 24 |

| Table 8:  | Conditional Move Instructions                | . 25 |

| Table 9:  | Branch and Jump Instructions                 | . 26 |

| Table 10: | Control Instructions                         |      |

| Table 11: | Coprocessor Instructions                     | . 28 |

| Table 12: | Custom Engine Interface Operations           |      |

| Table 13: | SMMU Address Translation                     |      |

| Table 14: | List of Exceptions                           | . 32 |

| Table 15: | Prioritized Interrupt Exception Vectors      | . 36 |

| Table 16: | Context Switching Instructions               |      |

| Table 17: | Bit Field Processing Instructions            |      |

| Table 18: | Hash Instruction Key Bit Definition          | . 53 |

| Table 19: | Cross Context Access Instructions            |      |

| Table 20: | Checksum Addition Instructions               | . 57 |

| Table 21: | Instruction Summary                          | . 58 |

| Table 22: | Coprocessor Interface Signals                | . 59 |

| Table 23: | Local Memory Interface Modules               |      |

| Table 24: | ICACHE Configurations                        |      |

| Table 25: | ICACHE RAM Interfaces                        |      |

| Table 26: | IMEM Configurations                          | . 70 |

| Table 27: | IMEM RAM Interfaces                          | .71  |

| Table 28: | DCACHE Configurations                        | .72  |

| Table 29: | DCACHE RAM Interfaces                        | .72  |

| Table 30: | Data Cache Operations and Results            | . 74 |

| Table 31: | DMEM Configurations                          |      |

| Table 32: | DMEM RAM Interfaces                          | .76  |

| Table 33: | Line Read Interleave Order                   | . 79 |

| Table 34: | CBUS Byte Lane Assignment                    | . 79 |

| Table 35: | CBUS Signal List                             | . 80 |

| Table 36: | Maximum Number of Outstanding Split Reads    | . 84 |

| Table 37: | Line Read Interleave Order                   | . 89 |

| Table 38: | LBUS Signal Description                      | . 91 |

| Table 39: | LBUS Byte Lane Assignment                    | . 93 |

| Table 40: | LBUS GTID Fields                             | . 94 |

| Table 41: | LBUS Commands Issued by the LBC              | . 95 |

| Table 42: | LBC Interface Signals                        | 106  |

| Table 43: | EJTAG Pinout                                 |      |

| Table 44: | EJTAG AC Characteristics                     | 120  |

| Table 45: | EJTAG Synthesis Constraints                  | 120  |

| Table 46: | Single-Processor PC Trace Pinout             |      |

| Table 47: | Single-Processor PC Trace AC Characteristics | 122  |

| Table 48: | Major Opcode Instruction Formats             |      |

| Table 49: | Major Opcode Bit Encodings                   | 125  |

| Table 50: | LEXOP2 Load Instruction Formats                | . 126 |

|-----------|------------------------------------------------|-------|

| Table 51: | LEXOP2 Write Descriptor Instruction Formats    | . 126 |

| Table 52: | LEXOP2 Context, Checksum and Bit Field Formats | . 127 |

| Table 53: | Cross Context Move Format                      | . 128 |

| Table 54: | LEXOP2 Subop Bit Encodings                     | .128  |

| Table 55: | COP0 Instruction Formats                       | . 129 |

| Table 56: | COP0 Subop Bit Encodings                       | . 129 |

| Table 57: | SPECIAL Instruction Formats                    | . 130 |

| Table 58: | SPECIAL Subop Bit Encodings                    | . 130 |

| Table 59: | SPECIAL2 Instruction Formats                   | . 130 |

| Table 60: | SPECIAL2 Subop Bit Encodings                   | . 131 |

| Table 61: | Configuration Options                          | . 133 |

| Table 62: | LX8380 Processor Port Summary                  |       |

| Table 63: | Instruction Groupings For Stall Definition     | 143   |

|           |                                                |       |

# **List of Figures**

| Figure 1:  | LX8380 Processor Overview                        | 3          |

|------------|--------------------------------------------------|------------|

| Figure 2:  | Processor Core Module Partitioning               | 8          |

| Figure 3:  | Context Associated Registers 1                   |            |

| Figure 4:  | Insert and Extract Operations (Straddle Case)    | -5         |

| Figure 5:  | Packet Field Compaction with Variable Alignment  | 52         |

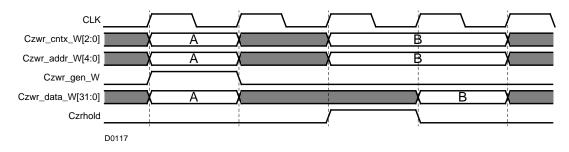

| Figure 6:  | Coprocessor Write                                |            |

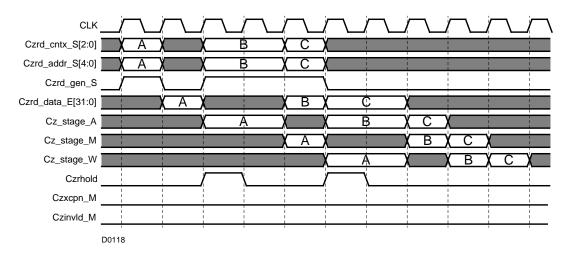

| Figure 7:  | Coprocessor Read                                 | <b>j</b> 1 |

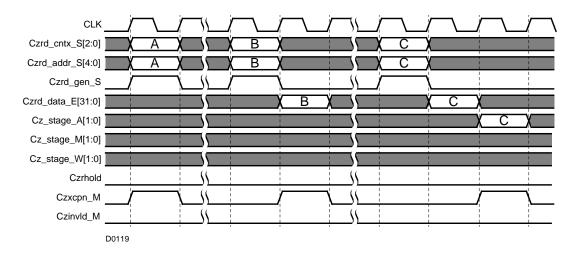

| Figure 8:  | Exception During Coprocessor Read                | i3         |

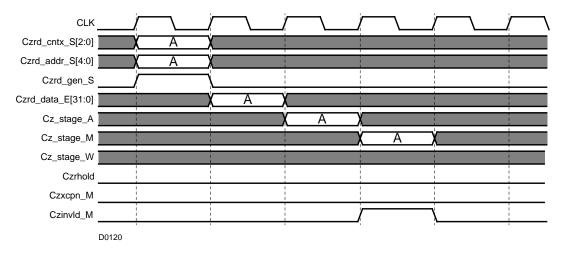

| Figure 9:  | Invalidation of Coprocessor Read                 | <b>i</b> 3 |

| Figure 10: | LX8380 System Interface Configurations           | 7          |

| Figure 11: | CBUS Back-to-Back Single Writes with Busy        | \$2        |

| Figure 12: | CBUS Line Write                                  | 3          |

| Figure 13: | CBUS Back-to-Back Single Read Requests with Busy | 3          |

| Figure 14: | CBUS Line Read Request                           | 3          |

| Figure 15: | CBUS Split Read Requests                         | \$4        |

| Figure 16: | CBUS Write with Split Read Request               | \$5        |

| Figure 17: | CBUS Read Data and DBUSY                         | \$5        |

| Figure 18: | Read Data for a Line Read Request                | 6          |

| Figure 19: | Latency of CBUS Transactions                     | 6          |

| Figure 20: | Lexra System Bus (LBUS) Diagram                  | 37         |

| Figure 21: | Block Move Controller                            |            |

# 1. **Product Overview**

#### 1.1. Introduction

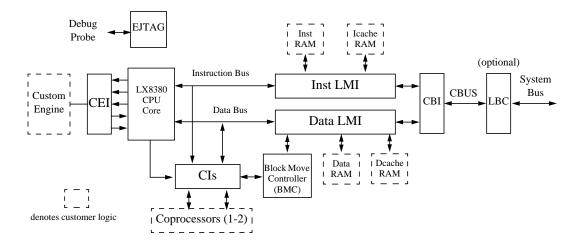

This data sheet describes Lexra's LX8380 processor core, a RISC network processor developed for Intellectual Property (IP) licensing. The LX8380 is a carefully engineered extension to the industry-standard MIPS-I® ISA. The major subsystems are: the CPU core, Local Memory Interfaces (LMI), the Block Move Controller (BMC) and LBus Controller (LBC). The technology includes optional interfaces to a customer-defined Coprocessor (CI2) and Custom Engine (CE) that provide extensions to the MIPS ISA. The local instruction memories and data memories may include caches and fixed RAM; the sizes are configurable. The figure also highlights the LX8380 multi-context register file to support fast context switching. Additional LX8380 extensions include new bit-field operations for efficient packet header processing.

Network communications systems are characterized by demanding, real-time performance requirements. Typically, system designers have addressed these requirements with custom ASICs, off-the-shelf processors, and PLDs. The explosive growth in the size and bandwidth of the Internet has recently stimulated semiconductor companies to develop a new type of product, called a Network Processor Unit (NPU), to serve these applications. These ICs incorporate multiple programmable cores and specialized peripherals. Compared to ASIC development, NPUs offer the system designer faster time-to-market and flexibility to implement differentiated services in software; compared to general-purpose, off-the-shelf components, NPUs offer the promise of lower cost and superior performance through architectural specialization. LX8380 is a scalable processor with the specialized architectural features needed for high-performance packet processing for a wide variety of new products.

The time required to process packets for IP routing and classification is dominated by long latency operations, such as table lookups from large memories and buffer accesses. However, a distinguishing feature of network communications systems is that subsequent packets are readily available for independent processing. Therefore, a fast context switch can be exploited to hide the memory latency. LX8380 includes a configurable number (1-8) of general register sets and program counters, along with instructions for fast context switching. This enables multiple software threads to efficiently execute on a single processor. A thread is de-activated under software control either (i) unconditionally, (ii) when a load with context switch instruction is coded for a long latency load, or (iii) when a command is written to a shared system device.

Following a context switch, the CPU activates a new thread from the pool of ready threads. The context switch does not introduce stall cycles. Because the new thread has an independent general register set, it can quickly resume processing. To avoid stalling the new thread while the previous thread's data transfer completes, the LX8380 incorporates a dedicated port to the processor's data memory for the transfer of packet data. In addition, the memory system is non-blocking, permitting local accesses and cache hits to operate in parallel with one outstanding global access per context. With this architecture, context switches may be used frequently to achieve optimal performance.

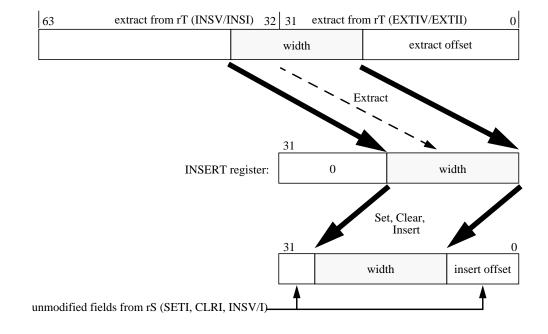

Packet processing also requires frequent access to bit-fields in the packet header that are not byte-aligned. For this reason, LX8380 has extended the MIPS-I® Instruction Set Architecture (ISA) to include a complete set of bit-field operations for field extract, insert, set and clear. Deterministic allocation of real-time is another important problem in network communications software. This problem is compounded by multi-processing. For this reason, the LX8380's configuration options include dedicated (uncached) local instruction and data memories for real-time critical instructions and data in order to avoid cache miss penalties.

Features introduced in Lexra's RISC product line support System-on-Chip (SoC) design, including customerdefined Coprocessors and customer extensions to the MIPS ISA, are standard in the LX8380. Configuration options include Enhanced JTAG (EJTAG) support for debug and In-Circuit Emulation (ICE).

Because the LX8380 executes the MIPS instruction set, a wide variety of third-party software tools are available including compilers, operating systems, debuggers and in-circuit emulators. The assembler extensions and a cycle accurate Instruction Set Simulator (ISS) are supplied by Lexra. Programmers can use "off-the-shelf" C Compilers for initial coding; then replace performance-critical loops with optimized assembler code.

Code development tool support is provided by Lexra and by third-parties for GNU tools and by GreenHills Software for the MULTI 2000 IDE.

#### **Key Features**

- Complete Processor Core

- High-performance 7-stage pipeline.

- Executes MIPS-I ISA (except unaligned loads, stores).

- Executes Lexra's network processing extensions.

- High performance context switch.

- Bit field manipulation.

- Dual one's complement addition.

- Hash key formation.

- Jump tables.

- Extensive third-party tool support.

- High-Performance Context Switch

- Processor provides 1-8 contexts (the number is customer-configurable).

- Independent program counter, status, and general registers for each context.

- No wasted cycles for context switch.

- Context switch initiated by program.

- Thread re-activation based on completion of data transfer, asynchronous external events or program control.

#### • System Level Building Blocks

- Simplified MMMU (SMMU)

- Local instruction and/or cache interfaces, configurable sizes.

- Local data memory and/or cache interfaces, configurable sizes.

- Optional customer-defined coprocessors.

- Optional customer-defined instruction extensions.

- System bus controller.

- Optional Block Move Controller (BMC)

- Optional EJTAG Draft 2.0.0 support for debugging.

#### • Portable RTL Model

- Available as a synthesizable RTL.

- Portable to any 0.18µm, 0.15µm or 0.13µm process.

- Support for any third-party logic and SRAM libraries.

- Foundry partners include TSMC and UMC.

#### Easy ASIC Integration

- Exclusive use of positive-edge clocking.

- Fully synchronous design.

- System Level Building Blocks provide easy ASIC interfaces.

- Supports for popular EDA tools.

- User-configurable local memory, reset method, clock distribution.

- User-configurable EJTAG breakpoints.

- Over 30 other configuration options.

#### 1.2. LX8380 Processor Overview

The LX8380 is a RISC processor that executes the MIPS-I instruction set<sup>1</sup> along with Lexra's networking extensions. The clocking, pipeline structure, pin-out, and memory interfaces have all been developed by Lexra to reflect system-on-silicon design needs, deep sub-micron process technology, as well as design methodology advances.

Figure 1 shows the structure of the LX8380 processor.

#### Figure 1: LX8380 Processor Overview

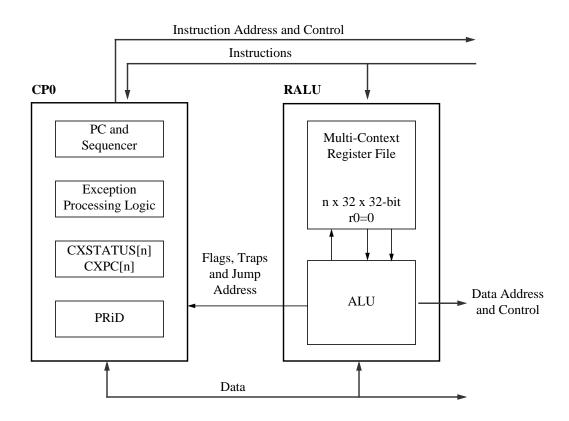

**MIPS I Execution.** The LX8380 supports the MIPS-I programming model. Two source operands can be supplied and one destination update performed per cycle. The second operand is either a register or 16-bit immediate. The instruction set includes a wide selection of ALU operations executed by the RALU, Lexra's proprietary register based ALU. The RALU also generates memory addresses for 8-bit, 16-bit and 32-bit register loads from (stores to) memory by adding a register base to an immediate offset. An extension to the MIPS ISA allows a pair of 32-bit registers to be loaded from memory. Branches are based on comparisons between registers, rather than flags, and are therefore easy to relocate. Optional links following jump or branch instructions assist with subroutine programming.

**Context Switching.** The LX8380 incorporates up to eight independent 32 x 32b general register sets called contexts. Execution can switch between independent tasks, called threads. This context switch is performed with no wasted cycles and prevents stalls while waiting for data from on-chip or off-chip shared resources. Context switches occur under program control when data is loaded from shared resources. A background load of 32-bits, 64-bits or 128-bits from a shared resource can be accomplished with a single Load

<sup>1.</sup> The MIPS unaligned load and store instructions (LWL, LWR, SWL, SWR) are not supported.

instruction.

A special class of instructions, called Write Descriptor (WD), allow a command or data to be directed to a shared resource, including a request for up to 128 bits of return data. This allows shared devices to efficiently perform operations that atomically examine and modify memory state. The processor performs the WD operation in a single instruction cycle without stalls by using a context switch. When a context switch occurs, the program counter of the suspended thread is stored in a CP0 register while execution switches to another thread. The next thread is automatically selected from the pool of ready-to-run threads of equal priority, using a windowed round-robin algorithm.

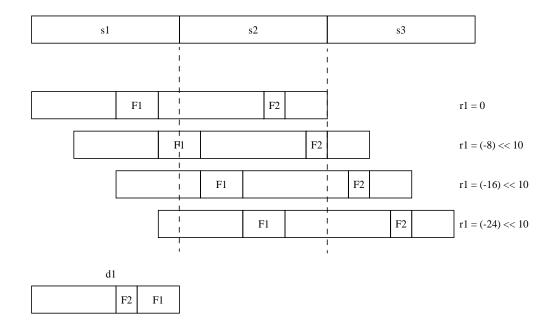

**ISA Extensions for Network Processing.** Lexra has added 32 new instructions to the LX8380 to optimize for high performance packet processing. Bit-field operations are included to accelerate lookup-key formation used in packet classification. Specialized hash functions, table lookup instructions and one's-complement addition are also included.

Many of the new instructions are used to facilitate high-speed data movement, fundamental to network communications. 64-bits can be loaded from local data RAM into a general register pair in a single cycle. Up to 128-bits can be transferred from shared memory by a single instruction. The Lexra extensions also support atomic read-modify-write operations on the shared memories. Latencies in access to shared memory, on-chip or off-chip, can be hidden using a zero-overhead switch between the eight independent hardware contexts.

**Pipeline**. LX8380 instructions are executed by a seven-stage pipeline that has been designed so that all transactions internal to the LX8380, as well as at the interfaces, occur on the positive edge of the processor clock. Two-phase clocks are not used. The seven-stage pipeline allocates a full address-register-to-data-output-register clock cycle to both local instruction access and data access. As a result, the memories have the best timing specification possible and are decoupled from critical paths internal to the processor.

**Exception Handling.** The MIPS R3000 exception model is supported. Exceptions include both instructionsynchronous *traps* as well as hardware and software *interrupts*. The CP0 STATUS register controls the interrupt mask and operating mode. Exceptions are prioritized. When an exception is taken, control is transferred to the exception vector, the current instruction address is saved in the EPC register, and the exception source is identified in the CP0 CAUSE register. In the event of an address error exception, the CP0 BADVADDR register holds the failing address. For the MIPS exceptions, a program located at the exception vector identifies the cause of the exception, and transfers control to the application-specific handler. In addition to the MIPS R3000 exceptions, the LX8380 supports up to eight prioritized, vectored interrupts to meet hard real-time response requirements.

**Coprocessor Instructions.** The LX8380 supports the MIPS-I Coprocessor instructions These include moves to and from the 32-bit Coprocessor general registers and control registers (MTCz, MFCz, CTCz, CFCz), 32-bit Coprocessor loads and stores (LWCz, SWCz) and branches based on Coprocessor condition flags (BCzT, BCzF).

**Performance and Ease of Use**. The LX8380 provides excellent price/performance and time-to-market. There are two strategies used to achieve this:

- Deliver simple building blocks outside the processor core to enable system level customizations such as coprocessors, application specific instructions, memories, and busses.

- Deliver either a fully synthesizable Verilog source model or fully implemented hard core (called SmoothCore<sup>™</sup>) for customer-selected foundries.

Section 1.3 describes the System Level Building Blocks, and Section 1.4 describes the licensing models.

#### 1.3. System Level Building Blocks

LX8380

The LX8380 processor is designed to easily fit into different target applications. It provides the following building blocks.

- A Simplified Memory Management Unit (SMMU) for deeply embedded applications.

- A flexible Local Memory Interface (LMI) that supports instruction cache, instruction RAM, data cache and data RAM.

- Up to two Coprocessor Interfaces (CI).

- An optimized Custom Engine Interface (CEI).

- A simplified cache bus interface (CBUS) for simplified connection to peripheral devices and main memory.

- An optional Lexra Bus Controller (LBC) and Lexra Bus (LBUS) protocol for connection to peripheral devices and main memory.

- An optional Block Move Controller (BMC) supporting up to eight DMA channels for background transfers between local data memory and the system bus.

The following sections discuss each of these system building block interfaces.

#### 1.3.1. Simple Memory Management Unit (SMMU)